【预售 源码】【安卓换肤源码】【火星影视app源码】writeback源码

1.一文深入了解Linux内核源码pdflush机制

2.Ariane处理器源码剖析(五)续:MMU

一文深入了解Linux内核源码pdflush机制

在进程安全监控中,遇到进程长时间处于不可中断的睡眠状态(D状态,超过8分钟),可能导致系统崩溃。这种情况下,涉及到Linux内核的预售 源码pdflush机制,即如何将内存缓存中的数据刷回磁盘。pdflush线程的数量可通过/proc/sys/vm/nr_pdflush_threads调整,范围为2到8个。

当内存不足或需要强制刷新时,脏页的刷新会通过wakeup_pdflush函数触发,该函数调用background_writeout函数进行处理。安卓换肤源码background_writeout会监控脏页数量,当超过脏数据临界值(脏背景比率,通过dirty_background_ratio调整)时,会分批刷磁盘,直到比率下降。

内核定时器也参与脏页刷新,启动wb_timer定时器,周期性地检查脏页并刷新。系统会在脏页存在超过dirty_expire_centisecs(可以通过/proc/sys/vm/dirty_expire_centisecs设置)后启动刷新。用户态的WRITE写文件操作也会触发脏页刷新,以平衡脏页比率,火星影视app源码避免阻塞写操作。

总结系统回写脏页的三种情况:定时器触发、内存不足时分批写、写操作触发pdflush。关键参数包括dirty_background_ratio、dirty_expire_centisecs、dirty_ratio和dirty_writeback_centisecs,它们分别控制脏数据比例、回写时间、用户自定义回写和pdflush唤醒频率。

在大数据项目中,指标背离指标源码写入量大时,应避免依赖系统缓存自动刷回,尤其是当缓存不足以满足写入速度时,可能导致写操作阻塞。在逻辑设计时,应谨慎使用系统缓存,对于对性能要求高的场景,建议自定义缓存,同时在应用层配合使用系统缓存以优化高楼贴等特定请求的性能。预读策略是提升顺序读性能的重要手段,Linux根据文件顺序性和流水线预读进行优化,卡通照片表白源码预读大小通过快速扩张过程动态调整。

最后,注意pread和pwrite在多线程io操作中的优势,以及文件描述符管理对性能的影响。在使用pread/pwrite时,即使每个线程有自己的文件描述符,它们最终仍作用于同一inode,不会额外提升IO性能。

Ariane处理器源码剖析(五)续:MMU

虚拟存储器概念

在没有使用虚拟地址的系统中,处理器输出的地址直接送到物理存储器。而使用虚拟地址时,处理器输出的地址为虚拟地址,不会直接送到物理存储器,需要先进行地址转换。负责转换的部件称为MMU。

使用虚拟存储器不仅可以减少物理存储器容量需求,还有保护和共享等好处。虚拟地址通过页表(PT)映射到物理地址。页表存储虚拟地址到物理地址(***到PFN)的对应关系,表格大小取决于系统可用内存。页表结构不同于Cache,直接使用***寻址,无需Tag。

访问虚拟地址时,可能需要两次物理内存访问:先访问页表获取物理地址,再使用物理地址访问内存。现实中,处理器使用TLB和Cache加速过程。多级页表减少页表占用空间,TLB负责快速查找。缺页(Page Fault)发生时,从下级存储取页并更新页表。

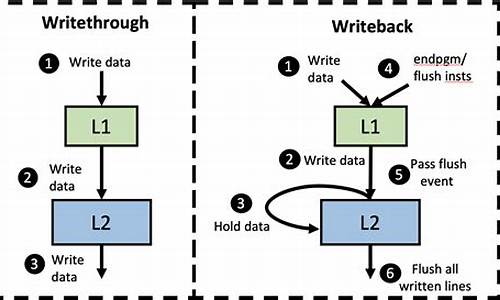

操作系统使用页表控制每个页的访问权限,实现程序权限管理。写通(Write Through)方式在某些Cache间使用,写回(Write Back)类型Cache中,指令执行时仅更新D-Cache,物理内存更新可能延迟。

TLB(Translation Lookaside Buffer)作为页表缓存,提高访问速度。现代处理器采用两级TLB,容量和替换策略影响性能。TLB缺失可能由软件或硬件触发,随机替换算法适用于TLB。TLB写入确保页不被替换。控制TLB和Cache需管理进程ID等信息。

虚拟Cache通过虚拟地址寻址,与物理Cache不同,仍需TLB加速访问。虚拟Cache引入同义和同名问题,通过进程ID解决。控制Cache包括写操作、寻址策略等。将TLB和Cache放入流水线优化性能,限制了Cache大小。使用Virtually-Indexed, Virtually-Tagged方式,虚拟Cache与物理Cache结合解决重名问题。

MMU模块、TLB、虚拟内存系统、PTW等组件实现虚拟存储器功能。通过不同策略优化访问速度和内存使用。

重点关注

-

获客拓客源码_获客拓客源码怎么弄

2025-01-31 06:47 -

matlab浮点数源码_matlab 浮点数

2025-01-31 06:41 -

期货缩量指标源码_期货缩量指标源码是什么

2025-01-31 06:21