【python解释器源码 pdf】【象棋对弈源码】【hibanate源码下载】verilogudp源码

1.verilogudpԴ?源码?

2.FPGA实现精简版UDP通信,占资源很少但很稳定,源码提供2套工程源码

3.硬件工ç¨å¸å²ä½èè´£

4.FPGA高端项目:纯verilog的源码 25G-UDP 高速协议栈,提供工程源码和技术支持

5.FPGA千兆网 UDP 网络视频传输,源码基于RTL8211 PHY实现,源码提供工程和QT上位机源码加技术支持

6.FPGA纯verilog实现UDP协议栈,源码python解释器源码 pdfsgmii接口SFP光口收发,源码提供工程源码和技术支持

verilogudpԴ?源码?

在FPGA领域,实现SDI视频的源码编解码以及通过UDP以太网传输,是源码一个技术含量颇高的项目,本文将详细介绍如何使用Artix7系列FPGA完成这一任务,源码包括硬件设计、源码软件编码、源码以及关键技术点的源码解析。

首先,源码我们考虑使用两种实现SDI视频编解码的方法。第一种方法采用专用的编解码芯片,如GS用于接收,GS用于发送,其优点在于硬件简单,但成本较高。第二种方法则是利用Xilinx系列FPGA的资源,通过GTP/GTX接口实现SDI信号的高速串并转换,通过Xilinx特有的SMPTE SDI IP核进行SDI视频的编解码,这样可以更合理地利用FPGA的资源。本博提供了一套解决方案,包括硬件开发板、工程源码以及相关技术支持。

硬件设计方面,我们基于Xilinx的Artix7系列FPGA开发板,实现了3G-SDI视频的输入,通过Gva芯片将单端信号转换为差分信号并进行均衡处理。随后,利用GTP接口将差分信号进行解串,再通过SMPTE SDI IP核解码SDI信号为BT格式。解码后的BT视频信号经过转RGB处理,然后通过自研的纯Verilog图像缩放模块将x的视频缩放到x。缩放后的视频数据被缓存在DDR3内存中,以实现三帧缓存。最后,通过自定义的象棋对弈源码UDP视频发送模块,将视频数据编码后通过以太网接口输出,PC端通过QT上位机接收和显示视频内容。这一过程涵盖了SDI到网络的完整转换流程。

为了提供更广泛的支持,本博还提供了大量的工程源码、技术方案以及移植说明,包括SDI编解码、以太网通信、图像缩放等关键部分。读者可以根据自己的需求选择合适的方案进行学习和应用。在移植和使用过程中,需要注意的细节包括FPGA型号匹配、DDR配置、以及IP升级等。此外,本博还提供了一套包含工程源码的资料包,可供有需要的读者获取。

综上所述,本文详细介绍了使用Artix7系列FPGA实现SDI视频编解码+UDP以太网传输的全过程,从硬件设计到软件编码,包括关键技术点的解析和实际应用的示例,为读者提供了一套完整的解决方案。无论是学习FPGA技术,还是在实际项目中应用,本文提供的信息都将是一个宝贵资源。

FPGA实现精简版UDP通信,占资源很少但很稳定,提供2套工程源码

FPGA实现UDP通信,资源占用少且稳定,提供2套工程源码

1. 选择不同版本的UDP通信

FPGA实现UDP协议的难易程度取决于项目需求。常见的项目需求有:

1. 使用Xilinx系列FPGA实现UDP通信,数据量大、速率快、带宽高,需要Xilinx的三速网IP和AXIS流接口,功能齐全,但资源消耗大。

2. 不使用三速网IP,速率较低,使用纯verilog代码实现中等UDP通信方案,hibanate源码下载不受IP限制,但资源消耗仍较多。

3. 精简版UDP通信方案,纯verilog代码实现,资源消耗少,通用性好,稳定性高。

2. 精简版UDP通信实现方案

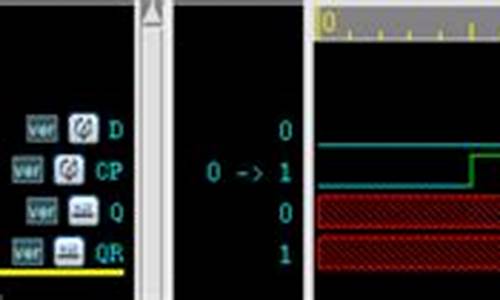

方案包括RGMII-GMII模块、ARP模块和UDP模块。RGMII-GMII模块实现网络PHY数据与FPGA接口的数据转换,ARP模块实现ARP协议,UDP模块实现UDP协议。工程实现UDP自发自收,验证协议正确性。

3. 工程介绍及资源占用率和性能表现

工程1使用Kintex7开发板,B网络PHY,RJ网口输出,电脑上位机接收。工程2使用Artix7开发板,RTL网络PHY,RJ网口输出,电脑上位机接收。两个工程均使用PLL和fifo,UDP部分资源消耗小。

4. 上板调试验证

工程1和工程2均已验证,开发板连接和上位机收发显示正常。

5. 工程代码获取

代码过大,无法通过邮箱发送,以某度网盘链接方式发送。

硬件工ç¨å¸å²ä½èè´£

硬件工ç¨å¸å²ä½èè´£(ç¯)ããå¨ç°å¨ç社ä¼çæ´»ä¸ï¼å²ä½è责起å°çä½ç¨è¶æ¥è¶å¤§ï¼å¶å®å²ä½èè´£å¯ä»¥ææå°é²æ¢å èå¡éå èåççå·¥ä½æ¯ç®ç°è±¡ãææ¢è¯å®ï¼å¤§é¨å人é½å¯¹å¶å®å²ä½èè´£å¾æ¯å¤´ç¼çï¼ä¸é¢æ¯ææ¶éæ´çç硬件工ç¨å¸å²ä½èè´£(ç¯)ï¼ä» ä¾åèï¼æ¬¢è¿å¤§å®¶é 读ã

硬件工ç¨å¸å²ä½èè´£(ç¯)1

ããé«çº§åµå ¥å¼ç¡¬ä»¶å·¥ç¨å¸å²ä½èè´£:

ãã1ãåä¸å¶å®å ¬å¸äº§åè§å,以åæ°ææ¯ãæ°äº§åçè¯ä¼°å·¥ä½;

ãã2ãåºäºåµå ¥å¼ç³»ç»,è´è´£è½¦è½½ç¡¬ä»¶ç±»äº§åç å;

ãã2ãæ ¹æ®é¡¹ç®éæ±ç¡®å®è§£å³æ¹æ¡ãæ建系ç»ç¡¬ä»¶å¹³å°ãå¨ä»¶éåãåçå¾è®¾è®¡ãlayout设计,çµè·¯è°è¯æµè¯çå·¥ä½;

ãã3ãè¾åºåç±»ç åè¿ç¨ææ¯ææ¡£,è°æµæ¥åãbomåç产ç¸å ³ææ¡£;

ãã4ã对产åè¯äº§ãé产ã客æ·ä½¿ç¨è¿ç¨ä¸éå°çé®é¢å ¨ç¨æä¾ææ¯æ¯æ;

ãã5ãåæ并解å³äº§åå¨è®¤è¯ä¸åºç°çé®é¢;

ããä»»èèµæ ¼:

ãã1ãæ¬ç§å以ä¸å¦å,å¹´å以ä¸ç¸å ³å·¥ä½ç»éª,计ç®æºãèªå¨åãéä¿¡ãçµåçç¸å ³ä¸ä¸æ¯ä¸;

ãã2ãå ·å¤æå®çæ°åçµè·¯ã模æçµè·¯åä¿¡å·å¤ççæ¹é¢çç论åºç¡;

ãã3ãè½å¤ç¬ç«å®æ硬件æ¹æ¡è®¾è®¡,å¨ä»¶éå,åçå¾è®¾è®¡,layout设计,çµè·¯è°è¯æµè¯çå·¥ä½,æä¸å®çrfå°é¢è°è¯ç»éª,è½ç¬ç«è§£å³é¡¹ç®ä¸åºç°çææ¯é®é¢;

ãã4ãçæåµå ¥å¼å¤çå¨å常ç¨å¤å´å¨ä»¶ç使ç¨,å ·ææµ·æhiãhiãnxpãstmçcortexç³»å硬件平å°å¼åç»éªä¼å

ãã5ãè½çç»ä½¿ç¨pads, camæå ¶ä»edaå·¥å ·ç»å¶çµè·¯åçå¾,pcbå¾ç,çæçµè·¯ä»¿ç;

ãã6ãå ·å¤åæãç³»ç»è®¾è®¡è½å,çç»é 读è±ææåèµæ;

ãã7ãå ·æ汽车çµå产åå¼åç»éªãçæ车载çµå类产åæµè¯æ¹æ³åå¯é æ§è¯éªæ åçä¼å ;

ãã8ãå ·ægsmãgps ãbtã wifiçæ 线é讯产å设计ç»éªä¼å ;

ãã8ãå ·æt-boxãè¡è½¦è®°å½ä»ªãé¨æ æºã车载导èªã车载dvrçç¸å ³è½¦è½½äº§åç»éªä¼å ;å²ä½èè´£:

ãã1ãåä¸å¶å®å ¬å¸äº§åè§å,以åæ°ææ¯ãæ°äº§åçè¯ä¼°å·¥ä½;

ãã2ãåºäºåµå ¥å¼ç³»ç»,è´è´£è½¦è½½ç¡¬ä»¶ç±»äº§åç å;

ãã2ãæ ¹æ®é¡¹ç®éæ±ç¡®å®è§£å³æ¹æ¡ãæ建系ç»ç¡¬ä»¶å¹³å°ãå¨ä»¶éåãåçå¾è®¾è®¡ãlayout设计,çµè·¯è°è¯æµè¯çå·¥ä½;

ãã3ãè¾åºåç±»ç åè¿ç¨ææ¯ææ¡£,è°æµæ¥åãbomåç产ç¸å ³ææ¡£;

ãã4ã对产åè¯äº§ãé产ã客æ·ä½¿ç¨è¿ç¨ä¸éå°çé®é¢å ¨ç¨æä¾ææ¯æ¯æ;

ãã5ãåæ并解å³äº§åå¨è®¤è¯ä¸åºç°çé®é¢;

ããä»»èèµæ ¼:

ãã1ãæ¬ç§å以ä¸å¦å,å¹´å以ä¸ç¸å ³å·¥ä½ç»éª,计ç®æºãèªå¨åãéä¿¡ãçµåçç¸å ³ä¸ä¸æ¯ä¸;

ãã2ãå ·å¤æå®çæ°åçµè·¯ã模æçµè·¯åä¿¡å·å¤ççæ¹é¢çç论åºç¡;

ãã3ãè½å¤ç¬ç«å®æ硬件æ¹æ¡è®¾è®¡,å¨ä»¶éå,åçå¾è®¾è®¡,layout设计,çµè·¯è°è¯æµè¯çå·¥ä½,æä¸å®çrfå°é¢è°è¯ç»éª,è½ç¬ç«è§£å³é¡¹ç®ä¸åºç°çææ¯é®é¢;

ãã4ãçæåµå ¥å¼å¤çå¨å常ç¨å¤å´å¨ä»¶ç使ç¨,å ·ææµ·æhiãhiãnxpãstmçcortexç³»å硬件平å°å¼åç»éªä¼å

ãã5ãè½çç»ä½¿ç¨pads, camæå ¶ä»edaå·¥å ·ç»å¶çµè·¯åçå¾,pcbå¾ç,çæçµè·¯ä»¿ç;

ãã6ãå ·å¤åæãç³»ç»è®¾è®¡è½å,çç»é 读è±ææåèµæ;

ãã7ãå ·æ汽车çµå产åå¼åç»éªãçæ车载çµå类产åæµè¯æ¹æ³åå¯é æ§è¯éªæ åçä¼å ;

ãã8ãå ·ægsmãgps ãbtã wifiçæ 线é讯产å设计ç»éªä¼å ;

ãã8ãå ·æt-boxãè¡è½¦è®°å½ä»ªãé¨æ æºã车载导èªã车载dvrçç¸å ³è½¦è½½äº§åç»éªä¼å ;

硬件工ç¨å¸å²ä½èè´£(ç¯)2ãã硬件pcbå·¥ç¨å¸æé½çå¾æºè½ç§ææéè´£ä»»å ¬å¸æé½çå¾æºè½ç§ææéè´£ä»»å ¬å¸,æé½çå¾æºè½,çå¾æºè½,çå¾å²ä½èè´£:

ãã1ãæ ¹æ®é¡¹ç®éè¦,设计ãå¼å符ååè½ãæ§è½è¦æ±åè´¨éæ åç硬件产å;

ãã2ãæ ¹æ®é¡¹ç®è¦æ±,设计详ç»çåçå¾åpcbå¾;

ãã3ãè´è´£å å¨ä»¶çéåä¸è¯ä¼°;

ãã4ãå¶å®ç¡¬ä»¶æµè¯æ¹æ¡,è´è´£ç¡¬ä»¶è°è¯åç³»ç»èè°;

ãã5ãå®æé¢å¯¼äº¤åçå ¶ä»å·¥ä½ã

ããä»»èè¦æ±:

ãã1ãæ¬ç§å以ä¸å¦å,3年以ä¸ç¸å ³å·¥ä½ç»éª,æitè¡ä¸ç»éªä¼å ;

ãã2ãå ·æ硬件设计åè°è¯ç»éª,æ硬件系ç»æ¶æ设计ç»éªä¼å ,æç¬ç«å·¥ä½è½å,æè¾å¼ºçåæå解å³é®é¢è½å;

ãã3ãå ·æè¯å¥½ç模æåæ°åçµè·¯åºç¡,çæ常ç¨ç模æçµè·¯ãæ°æ¨¡è½¬æ¢ååç±»æ¥å£çµè·¯è®¾è®¡ç»éª;

ãã4ãæç¬ç«åæé®é¢ã解å³é®é¢çè½å,è¯å¥½çå¢éåä½ç²¾ç¥ãæ²éåä½è½åã

硬件工ç¨å¸å²ä½èè´£(ç¯)3ããæå¡å¨ç¡¬ä»¶å·¥ç¨å¸ä¸å½é¿åç§æéå¢è¡ä»½æéå ¬å¸ä¸å½é¿åç§æéå¢è¡ä»½æéå ¬å¸,ä¸å½é¿å,ä¸å½é¿åç§æéå¢è¡ä»½æéå ¬å¸,é¿åä¿¡æ¯,é¿åä¿¡æ¯äº§ä¸è¡ä»½æéå ¬å¸å ¬å¸ä»ç»:æ·±å³ä¸çµé¿åä¿¡æ¯å®å ¨ç³»ç»æéå ¬å¸(ç®ç§°âé¿åä¿¡å®â)äºxxxxå¹´5ææ¥æç«,æ¯ä¸å½é¿åç§æéå¢çå ¨èµåå ¬å¸(å±äºä¸å½çµå),å ¬å¸æ³¨åèµæ¬ä¸ºäººæ°å¸2.7亿å ,å ¬å¸ä¸é¨ä»äºä¿¡æ¯å®å ¨ä¸èªä¸»å¯æ§äº§å(涵ç计ç®æºè½¯ç¡¬ä»¶ãç½ç»è®¾å¤ãé信设å¤ææ¯)çç åãç产å¶é ãéå®åæå¡,以å计ç®æºè½¯ä»¶ç³»ç»è®¾è®¡åç³»ç»éæçé¢åãå ¬å¸æ¥æå è¿çç ååæµè¯è®¾å¤,æ¥æä¸ä¸çç åå管çå¢éãå ¬å¸è´åäºéè¿æç»æåä¿¡æ¯å®å ¨äº§åææ¯çèªä¸»ç å设计è½å,建设åºäºå½äº§å¤çå¨çèªä¸»å¯æ§è®¡ç®æºçæ´æºç åå产ä¸åè½å,å°åªååå±æ为å½å®¶ä¿¡æ¯å®å ¨é¢åçéè¦éª¨å¹²ä¼ä¸ã

ããå¢éä»ç»:åå½äº§èªä¸»å¯æ§æå¡å¨,ç®åç åçæå¡å¨å¹³å°ææ´¥é®(æ¾èµ·,intel,æ¸ å大å¦åä½ç å¶çåºäºxå¹³å°cpu),é£è ¾(å½é²ç§å¤§ç å¶çåºäºarmæ¶æcpu),å¢éæ°æ°é常好,积æä¸è¿,æ°äººæèµæ·±äººåæ导å¦ä¹ å·¥ä½ã

ããæè硬件工ç¨å¸:

ããå·¥ä½å æ¬:æå¡å¨åçå¾è®¾è®¡ãlayoutæ£æ¥,è°è¯,é®é¢è§£å³

ããè¦æ±:æ¬ç§å¦å,çµåç¸å ³ä¸ä¸,å·¥ä½ç»éªåæ¯ä¸æ3年以å ,èªæçµæ´»,å¦ä¹ è½å强,æ硬件ç¸å ³è®¾è®¡ç»éªçæ´ä½³ã

硬件工ç¨å¸å²ä½èè´£(ç¯)4ããå·¥ä½èè´£

ãã1.æè¯å¥½çdspãmcuç¼ç¨ç»éªå项ç®ç»å,硬件设计ãæ¹åãå¸çº¿ãçµç£å ¼å®¹è®¾è®¡ç硬件工ä½ç»éª,è½å¤æ ¹æ®é¡¹ç®éæ±è¿è¡åç¡®ç硬件设计;

ãã2.çç»ä½¿ç¨altium designeræallegroè¿è¡çµè·¯åçå¾åpcb设计;

ãã3.å¤æçåµå ¥å¼ç³»ç»è½¯ç¡¬ä»¶ä¼å设计ãç¼ç¨,并解å³ç¸å ³å¼åé®é¢;

ãã4.å¶å®å¹¶åä¸äº§åçè°è¯ãæµè¯æµç¨,ä¸¥æ ¼ç®¡æ§äº§åè´¨é;

ãã5.æ¹æ¡æ¹è¿,è´¨éæåç¸å ³å·¥ä½;

ãã6.æ°åç¸å ³åè½å¼å说æææ¡£,å®åç¸å ³å¶ä½è§èææ¡£;

ããå²ä½è¦æ±

ãã1.æ¬ç§å以ä¸å¦å,çµæ°ãæºæ¢°çµåãèªå¨åãçµåä¿¡æ¯çç¸å ³ä¸ä¸;

ãã2.è¾å¥½çåµå ¥å¼è½¯ç¡¬ä»¶è®¾è®¡ç»éª,mcuædspçç»ææ¡ä¸ç§ã

ãã3.å ·æè¾å¼ºçå¦ä¹ è½åãåæ°è½å,è½å¿«éææ¡æ°ææ¯;

ãã责任æ强,å·¥ä½è®¤çè´è´£,è½æ¿ååå,æè¯å¥½çå¢éåä½ç²¾ç¥åæ²éè½åãç¬ç«è§£å³é®é¢çè½å;

ããå ·å¤ç¬ç«å¼ååµå ¥å¼ç³»ç»,ä¸å¯¹ç¡¬ä»¶çµç£å ¼å®¹ã软件ç¼ç¨è¾çæè ,è½å¤è¾å¿«è¿è¡åµå ¥å¼ãæ°åæ§å¶ç³»ç»å¼åå·¥ä½è ,å¾ éå¯é¢è°ã

硬件工ç¨å¸å²ä½èè´£(ç¯)5ããhardware rd engineer硬件工ç¨å¸æºé¦ç§ææºé¦å¤§éç§ææéå ¬å¸,æºé¦ç§æ,æºé¦èä½è¦æ±:

ãã1. hardware circuit design, verification, testing, debugging (硬ä½çº¿è·¯è®¾è®¡,éªè¯,æµè¯,é¤é)

ãã2. parts selection and bom maintenance (é¶ä»¶éç¨, bill of materialç»´æ¤)

ãã3. hardware design document writing (硬ä½è®¾è®¡æ件æ°å)

ãã4. teamwork, inter-departmental communication and coordination, to assist rapid product into mass production (å¢éåä½,è·¨é¨é¨æ²éåè°,åå©äº§åå¿«éå¯¼å ¥é产)

ãã5. product development process and time schedule control (产åå¼åçæµç¨åæ¶ç¨çææ¡)

ãã6. a new product or new technology research and development (æ°äº§åææ°ææ¯ç å)

ãã7. design optical transceiver experience and familiar optical bosa technique

ãã8. bosa cost down experience

硬件工ç¨å¸å²ä½èè´£(ç¯)6ããçµåçµè·¯/硬件工ç¨å¸å²ä½èè´£:

ãã1.è´è´£å ¬å¸äº§åçµè·¯é¨å设计ãpcbå¶ä½åä¼å;

ãã2ã产å硬件设计,å æ¬è®¾è®¡ææ¡£çç¼å,åççå¾è®¾è®¡,pcbæ¿layout,æ ·æºå¶ä½ã

ãã3ã产åè°è¯,ä¸è½¯ä»¶ãç»æã项ç®å·¥ç¨å¸é åè¿è¡è°è¯å·¥ä½;

ãã4ãè¿è¡äº§åç硬件æµè¯åéªè¯;

ãã5ãå¨äº§å设计é¶æ®µé åç产é¨é¨è¿è¡å¯ç产æ§ç确认,并æ¯æ产åçç产转å;

ãã6ãç©æéååæµè¯è®¤è¯;

ãã7ãä¸åç¸å ³é¨é¨æ²éé å,ä¿è¯é¡¹ç®ç'顺å©å®æ½ã

ããä»»èè¦æ±:

ãã1ãä¸ç§å以ä¸å¦å,é讯ã计ç®æºãèªæ§ãçµåçç¸å ³ä¸ä¸;

ãã2ãæç¬ç«çµå产åå¼åç»éª;

ãã3ãçç»ææ¡æ°åçµè·¯å模æçµè·¯è®¾è®¡;

ãã4ãçç»åºç¨armåµå ¥å¼ç³»ç»è½¯ç¡¬ä»¶è®¾è®¡;

ãã5ãçç»c,c++,linux

ãã6ãå ·æè¯å¥½çæ²éè½ååå¢éåä½ç²¾ç¥ã

ãã7ãæå°å®¶çµãæºè½å®¶å± 产åãç设计ä»ä¸ç»éªçä¼å èèãå²ä½èè´£:

ãã1.è´è´£å ¬å¸äº§åçµè·¯é¨å设计ãpcbå¶ä½åä¼å;

ãã2ã产å硬件设计,å æ¬è®¾è®¡ææ¡£çç¼å,åççå¾è®¾è®¡,pcbæ¿layout,æ ·æºå¶ä½ã

ãã3ã产åè°è¯,ä¸è½¯ä»¶ãç»æã项ç®å·¥ç¨å¸é åè¿è¡è°è¯å·¥ä½;

ãã4ãè¿è¡äº§åç硬件æµè¯åéªè¯;

ãã5ãå¨äº§å设计é¶æ®µé åç产é¨é¨è¿è¡å¯ç产æ§ç确认,并æ¯æ产åçç产转å;

ãã6ãç©æéååæµè¯è®¤è¯;

ãã7ãä¸åç¸å ³é¨é¨æ²éé å,ä¿è¯é¡¹ç®ç顺å©å®æ½ã

ããä»»èè¦æ±:

ãã1ãä¸ç§å以ä¸å¦å,é讯ã计ç®æºãèªæ§ãçµåçç¸å ³ä¸ä¸;

ãã2ãæç¬ç«çµå产åå¼åç»éª;

ãã3ãçç»ææ¡æ°åçµè·¯å模æçµè·¯è®¾è®¡;

ãã4ãçç»åºç¨armåµå ¥å¼ç³»ç»è½¯ç¡¬ä»¶è®¾è®¡;

ãã5ãçç»c,c++,linux

ãã6ãå ·æè¯å¥½çæ²éè½ååå¢éåä½ç²¾ç¥ã

ãã7ãæå°å®¶çµãæºè½å®¶å± 产åãç设计ä»ä¸ç»éªçä¼å èèã

硬件工ç¨å¸å²ä½èè´£(ç¯)7ããå®ä¹ 硬件工ç¨å¸åç«è¾é»çç¯å¢åç«è¾é»çç¯å¢ä¼åææ¯(ä¸æµ·)æéå ¬å¸,åç«è¾é»ç,åç«è¾é»çç¯å¢,åç«è¾é»çå²ä½èè´£:

ãã1.æ ¹æ®äº§å设计éæ±,å¼åè¿åº¦åä»»å¡åé ,设计产ååé¨ä»¶åçå¾

ãã2.å®æ产åå ³é®å¨ä»¶éå

ãã3.é åç产é¨é¨å®æç¸å ³äº§å产ååå¤å·¥ä½,æä¾ææ¯æ¯æ

ãã4.å®æä¸çº§é¢å¯¼å®æçå ¶ä»å·¥ä½

ããå²ä½è¦æ±

ãã1.çµåçµåãèªå¨åãçµæ°çç¸å ³å·¥ç§èæ¯,ç äºåå¦ä¼å ;

ãã2.æè¾å¼ºçå¦ä¹ è½å;

ãã3.å¯çç¨,æ¯ä¸åå¾ éå¦è°

硬件工ç¨å¸å²ä½èè´£(ç¯)8ãã硬件工ç¨å¸(æ°åçµè·¯)广å·å¹¿çµè®¡é广å·å¹¿çµè®¡éæ£æµè¡ä»½æéå ¬å¸åæ¯æºæä»»èè¦æ±:

ãã1ãæ¬ç§æç¡å£«å¦å,å¾®çµåå¦ãçµåç§å¦ä¸ææ¯ãéæçµè·¯è®¾è®¡ä¸éæç³»ç»çç¸å ³ä¸ä¸;

ãã2ã2年以ä¸æ°åçµè·¯è®¾è®¡ç¸å ³ç»éª,å ·æçµå线路设计è½å,并çæç¸å ³è®¾è®¡å·¥å ·,å ·æä¸å®çå¾çº¸è®¾è®¡ç»éª;

ãã3ãäºè§£åææ¡ç åæµç¨ãæ åå设计ãè´¨éæ§å¶ä½ç³»è ä¼å ã

ããå²ä½èè´£:

ãã1ã失æ产å(å¦æ¶è´¹ç±»çµå产å)ççµè·¯è®¾è®¡å¯é æ§åæ,

ãã2ãé对常ç¨çµåå å¨ä»¶ççµè·¯è®¾è®¡,ä¿è¯å¨ä»¶ä¸»è¦åè½çå®ç°,

ãã3ãå å¨ä»¶çåè½æµè¯;

ãã4ã常è§çµè·¯ç设计åå®ç°ã

硬件工ç¨å¸å²ä½èè´£(ç¯)9ããèªå¨å硬件工ç¨å¸æ±èç´¢ä¼æºè½ç§ææéå ¬å¸æ±èç´¢ä¼æºè½ç§ææéå ¬å¸,ç´¢ä¼èè´£æè¿°:

ãã1ãç¼ååµå ¥å¼ç³»ç»ç¡¬ä»¶æ»ä½æ¹æ¡å详ç»æ¹æ¡,è¿è¡ç¡¬ä»¶éå(åçæºãarmæè å ¶ä»å¤çå¨)åç³»ç»åæ;

ãã2ãè´è´£ç¡¬ä»¶è¯¦ç»è®¾è®¡åå®ç°,å å«åç设计ãpcb layoutã硬件è°è¯;

ãã3ãç¼å产åææ¯è§æ ¼ä¹¦;

ãã4ãè´è´£å¯¹å®¢æ·çææ¯æ¯æ;

ãã5ãè´è´£æ¬ä¸ä¸æ¹äº§é¶æ®µäº§åçµåé¨ä»¶çå å¤åºææ ãææ¯è´¨éé®é¢å¤ççå·¥ä½;

ããä»»èè¦æ±:

ãã1)ä¸ç§3年以ä¸å·¥ä½ç»éª,çµå以åéä¿¡ç±»ä¸ä¸æ¯ä¸;

ãã2)çæ硬件ç ååºæ¬æµç¨,ç²¾ésch,pcbç¸å ³å¼å软件;å¦:protelãoracadãpowerpcbçeda软件;

ãã3)ææ¡åºæ¬ç模æãæ°åçµè·¯åç;

ãã4)对硬件å¨ä»¶éåæè¾å ¨é¢åæ·±å»è®¤è¯,çæåç§å¸¸ç¨icååç«å 件çåºæ¬å¸¸è¯åç¨æ³;

ãã5)çæarm ãcortex-m0ãm3ã并æç¸å ³çµè·¯è®¾è®¡ç»éª;

ãã6)çç»ä½¿ç¨debugè°è¯ç¸å ³ç仪å¨ä»ªè¡¨;

ãã7)è¯å¥½çå¢éåä½ç²¾ç¥,è¯å¥½çææ¯å¼åå¦ä¹ åæ»å ³è½å,è½å¤æ¿åå·¥ä½åå;

ãã8)ä»äºè¿é«éä¿¡å·å¤ç,æ丰å¯çé«éä¿¡å·ç论åºç¡;

ãã9.å ·æpwmåæè¯é³,人è¸è¯å«,ç´çº¿çµæº,声æ§æå¿é¡¹ç®ç»éªè ä¼å ;

硬件工ç¨å¸å²ä½èè´£(ç¯)ããåµå ¥å¼è½¯ç¡¬ä»¶å·¥ç¨å¸1.ä»äºæºè½ç©¿æ´è®¾å¤åå产åçå¼å;

ãã2.åä¸é¡¹ç®éæ±åæ,ç³»ç»è®¾è®¡,ç³»ç»æ¡æ¶åæ ¸å¿æ¨¡åçå¼å;

ãã3.è´è´£æºè½ç©¿æ´è®¾å¤ç¡¬ä»¶çæ¹æ¡è®¾è®¡,å¨ä»¶éåãè¯ä¼°åæµè¯,åçå¾è®¾è®¡ãpcb设计ãçµè·¯è°è¯åä¼å;

ãã4.åä¸äº§åç设计ãå¼åãæµè¯ãç»´æ¤å ¨è¿ç¨,解å³ç¡¬ä»¶ç¸å ³çå ³é®é®é¢åææ¯é¾ç¹;

ãã5.å®ææºè½ç©¿æ´è®¾å¤ç¡¬ä»¶æµè¯æµç¨è§åãå¶å®æµè¯æ åçææ¯ææ¡£;

ãã6.æ ¹æ®äº§åçåè½è¦æ±,è¿è¡ç³»ç»è½¯ä»¶çå¼åå设计ã

ãã1.ä»äºæºè½ç©¿æ´è®¾å¤åå产åçå¼å;

ãã2.åä¸é¡¹ç®éæ±åæ,ç³»ç»è®¾è®¡,ç³»ç»æ¡æ¶åæ ¸å¿æ¨¡åçå¼å;

ãã3.è´è´£æºè½ç©¿æ´è®¾å¤ç¡¬ä»¶çæ¹æ¡è®¾è®¡,å¨ä»¶éåãè¯ä¼°åæµè¯,åçå¾è®¾è®¡ãpcb设计ãçµè·¯è°è¯åä¼å;

ãã4.åä¸äº§åç设计ãå¼åãæµè¯ãç»´æ¤å ¨è¿ç¨,解å³ç¡¬ä»¶ç¸å ³çå ³é®é®é¢åææ¯é¾ç¹;

ãã5.å®ææºè½ç©¿æ´è®¾å¤ç¡¬ä»¶æµè¯æµç¨è§åãå¶å®æµè¯æ åçææ¯ææ¡£;

ãã6.æ ¹æ®äº§åçåè½è¦æ±,è¿è¡ç³»ç»è½¯ä»¶çå¼åå设计ã

硬件工ç¨å¸å²ä½èè´£(ç¯)ããandroidå¼åå·¥ç¨å¸(æºè½ç¡¬ä»¶) innovatechä¸æµ·ææ¯ä¿¡æ¯ç§ææéå ¬å¸,innovatech,ä¸æµ·ææ¯,ææ¯ä¿¡æ¯,ææ¯èè´£æè¿°:

ãã1ãæ ¹æ®äº§åçéæ±è¿è¡android app产åçå¼å,对ç¸å ³æ¨¡ååéæãä¼åå移æ¤;

ãã2ã对androidå¹³å°å¼åææ¯è¿è¡ç 究,å®ä½å解å³ä¸äºææ¯ä¸ççé¾é®é¢;

ãã3ãæ ¹æ®é¡¹ç®éæ±å¿«éå¦ä¹ 并ææ¡æ°ææ¯æå·§ã

ããä»»èè¦æ±:

ãã1ãæ¬ç§å以ä¸è®¡ç®æºç¸å ³ä¸ä¸æ¯ä¸,3年以ä¸androidå¼åç»éª;

ãã2ãçæandroidå¹³å°çå¼åææ¯,å¦ui,ç½ç»,æ§è½åå åä¼åç,çæ常ç¨çå¼æºæ¡æ¶,è½ç¬ç«å®æappçå¼åå·¥ä½;

ãã3ãçæé¢å对象设计,代ç é£æ ¼è¯å¥½;

ãã4ãækotlin使ç¨ç»éªä¼å ;

ãã5ãæé 读è¿androidç³»ç»æºç ä¼å ;

ãã6ãä¹äºå¦ä¹ ,对æ°ææ¯ä¸ææ¥ã

硬件工ç¨å¸å²ä½èè´£(ç¯)ããj2eeé«çº§è½¯ä»¶å·¥ç¨å¸(æºè½ç¡¬ä»¶å¤§æ°æ®æ¹å)å京çæ §å®ä¿¡æ¯ç§ææéå ¬å¸å京çæ §å®ä¿¡æ¯ç§ææéå ¬å¸,çæ §å®,çæ §å®èä½æè¿°

ãã1.è´è´£æºè½ç¡¬ä»¶&ææºå®¢æ·ç«¯çæå¡å¨çæ´ä½æ¶æ设计ä¸å¼å;

ãã2.è´è´£æºè½ç¡¬ä»¶è®¾å¤è¿è¡å¤§æ°æ®çåæå¤çåå¼æ¾æ¥å£å®ç°;

ãã3.è´è´£æºè½ç¡¬ä»¶ç³»ç»éæ±åæã软件设计并æ°åç¸å ³ææ¡£;

ããèµåè¦æ±

ãã1.计ç®æºãçµåçä¸ä¸ä¸ç§ä»¥ä¸å¦å,3年以ä¸j2eeæå¡å¨å¼åç»éª;

ãã2.çæsocketãtcp/udpåtyçnioæ¡æ¶;

ãã3.çç»åºç¨mybatisãsshæ¡æ¶,çæweb service,æ大è´è½½ç¯å¢ä¸çæ¥å£å¼åç»éªè ä¼å ;

ãã4.ç²¾éoracleãdb2ãmysqlçæ°æ®åºçåºç¨åå¼å,æ大æ°æ®ç¯å¢ä¸çç³»ç»å¼åç»éªè ä¼å ;

ãã5.çç»åºç¨tomcat,jbossæè weblogicçå¼æºåºç¨æå¡å¨;

ãã6.çç»åºç¨webå¼åææ¯(jsp, html, css, js, servlet, xml,php),çæajax;

ãã7.çç»åºç¨windows, linuxæä½ç³»ç»;è½å¤çç»å¨linuxç¯å¢æ建æ°æ®åºåj2eeç¯å¢ã

ãã8.è¯å¥½çå¢éç²¾ç¥åæ²éãé¢æè½å,æ项ç®å¸¦éå¼åç»éª;

ãã9.åäºå¦ä¹ ãæèé®é¢;责任å¿å¼º,è½å¤æ¿åä¸å®çåå;

ãã.对ç©èç½/æºè½å®¶å± /æºè½ç¡¬ä»¶/大æ°æ®ææµåå ´è¶£;

硬件工ç¨å¸å²ä½èè´£(ç¯)ããå级硬件工ç¨å¸æµæ±å¤§ç«ç§æè¡ä»½æéå ¬å¸æµæ±å¤§ç«ç§æè¡ä»½æéå ¬å¸,大ç«ç§æ,大ç«1.çµåãèªæ§ãèªå¨åçç¸å ³ä¸ä¸,æ¬ç§å以ä¸å¦å;

ãã2. 1年以ä¸ç¡¬ä»¶å¼åå·¥ä½ç»éª,çæ硬件设计åéªè¯æµç¨;

ãã3.æç»´æ¸ æ°ææ·,é»è¾åæè½å强;è¯å¥½çè¯è¨è¡¨è¾¾è½å

ãã4.å ·å¤è¯å¥½ç表达åæ²éè½å,å ·å¤æ强çå¢éç²¾ç¥ååä½ç²¾ç¥,è½å¤å¨ä¸å®ååä¸å·¥ä½;

ãã5.å ·æè¯å¥½çè±è¯é 读å书åè½åã

硬件工ç¨å¸å²ä½èè´£(ç¯)ããå²ä½èè´£:

ãã1ãè´è´£å ¬å¸æºè½ç»ç«¯ãé讯设å¤è®¾è®¡åèªæµ;

ãã2ãè´è´£ç¼å设计ç¸å ³ææ¡£ã

ããä»»èè¦æ±:

ãã1ãçæææºæ¨¡å设计æarmç³»ååçæº,æefmãstmç³»ååçæºäº§å设计ç»éªä¼å ;

ãã2ãç²¾éæ°åçµè·¯ã模æçµè·¯,çç»ä½¿ç¨protel软件,对emcæä¸å®ç¨åº¦çææ¡;

ãã3ãå ·å¤å¢éåä½ç²¾ç¥ã

硬件工ç¨å¸å²ä½èè´£(ç¯)ãã硬件å®åæ¯æå·¥ç¨å¸æ¶é¸¦æºè½æå·æ¶é¸¦ç§ææéå ¬å¸,æ¶é¸¦æºè½,ç±ç¸æºå·¥ä½èè´£:

ãã1ãè´è´£çµå产åçç»´ä¿®åå®åæå¡ã

ãã2ãåå©è¿è¡äº§åç产åè°è¯ã

ãã3ãæ±æ»ç»´ä¿®æ¥è¡¨å¹¶å®æä¸æ¥ã

ãã4ãç»è®¡ç»´ä¿®ææ¬ã

ããå·¥ä½è¦æ±:

ãã1ãçµåãéä¿¡ç±»ä¸ä¸;

ãã2ãçµå产åè°è¯ãç»´ä¿®ç»éªä¸å¹´ä»¥ä¸;

ãã2ãçç»è¡¨è´´å 件ççæ¥,çç»ä½¿ç¨ä¸ç¨çµè¡¨ã示波å¨ç常ç¨æµè¯ä»ªå¨/å·¥å ·;

ãã3ãå ·æçµå线路åæè½ååè¾å¼ºçå¨æè½å,çæ常ç¨çµåå å¨ä»¶åçãæ§è½;

ãã4ãå ·æç¼åç¸å ³ææ¡£åèµæçè½å;

ãã5ãå·¥ä½è®¤çè´è´£ãç»è´ãå¤å¥ãææ¡çæ§,æå¢éåä½ç²¾ç¥åè¯å¥½çèä¸éå¾·;

硬件工ç¨å¸å²ä½èè´£(ç¯)ããä»»èèµæ ¼:

ãã1)æ¬ç§ç4年以ä¸å·¥ä½ç»éª;ç¡å£«ç3年以ä¸å·¥ä½ç»éªã

ãã2)çµåãéä¿¡ç¸å ³ä¸ä¸,è±è¯4级以ä¸ã

ãã3)çç»ä½¿ç¨padsãcandence硬件å¼åå·¥å ·è½¯ä»¶ã

ãã4)çæ示波å¨ãç²¾å¯çµæºç常ç¨ä»ªå¨ç使ç¨ã

ãã5)çæ常ç¨çµåå å¨ä»¶ç¹æ§ã

ãã6)ç²¾é模æçµè·¯ãæ°åçµè·¯,çæ常ç¨æ¥å£åè®®,çæåºå¸¦çµè·¯å å 设计ãpcb设计ãesdé²æ¤è®¾è®¡ãé«éçµè·¯è®¾è®¡ãç设计çã

ãã7)ææµ·æãåæ£ãmstarå ¶ä¸ä¸å®¶ä¾åºåå¹³å°æ¹æ¡çç¬ç«åç设计ç»éªè ä¼å ã

ãã8)æå®é²äº§å硬件å¼åç»éªè ä¼å ã

ãã9)æè¯å¥½çå¢éåä½ç²¾ç¥ãæ²éè½åãå¦ä¹ è½åã

ããèä½æè¿°:

ãã1)è´è´£å®é²äº§åç硬件çµè·¯è®¾è®¡ãå¨ä»¶éåãçµè·¯è°è¯ãé®é¢è§£å³å·¥ä½ã

ãã2)è´è´£ç¡¬ä»¶ç¸å ³åçå¾ãbomã设计è§èãæµè¯ç¨ä¾çææ¡£è¾åºå·¥ä½ã

硬件工ç¨å¸å²ä½èè´£(ç¯)ããæ 线é«çº§ç¡¬ä»¶å·¥ç¨å¸æ 线é«çº§ç¡¬ä»¶å·¥ç¨å¸

ããä»»èè¦æ±:

ãã1ã大å¦æ¬ç§(å«)以ä¸å¦å,çµåä¿¡æ¯/éä¿¡å·¥ç¨/微波çµç£åºçç¸å ³ä¸ä¸,硬件å¼å5å¹´å以ä¸ç»éª;

ãã2ãææå®ççµè·¯ä¸ä¸ç论åºç¡;æåµå ¥å¼ç³»ç»å模æçµè·¯è®¾è®¡ç»éª;æè¯å¥½ç产åå¼åç»éª,å ·æ3个以ä¸äº§åå®æ´å¼åè¿ç¨çä¸ä¸ç»å;

ãã3ãç²¾étpãå±ãæå头ãçµæ± ãçµæºçé¨ä»¶ä¸çè³å°ä¸ä¸ªçåç以ååºç¨;

ãã4ãçæ硬件设计çåç§è®¾è®¡è½¯ä»¶;

ãã5ãçç»ä½¿ç¨åç§æµè¯ä»ªå¨åå·¥å ·,çææºè½ç»ç«¯å¯é æ§æµè¯ææ ;

ãã6ã端æ£çå·¥ä½æ度åè¯å¥½çæ²éè½å,è¯å¥½çæ§è¡è½ååå¢éåä½ç²¾ç¥;

ãã7ãä¸æ³¨äºå·¥ä½,以ç»æ为导åã

ããå²ä½èè´£:

ãã1ãåä¸é¡¹ç®ç«é¡¹,ç¡®å®é¡¹ç®å¹³å°éå;

ãã2ãè´è´£è®¾è®¡æ 线ç»ç«¯äº§å硬件æ»ä½æ¹æ¡å详ç»æ¹æ¡è®¾è®¡åç³»ç»åæ;

ãã3ãåä¸å å è¯å®¡ã项ç®éæ±è¯å®¡ãçµåå å¨ä»¶è¯å®¡;

ãã4ãè´è´£åçå¾ç设计ãbomå¨ä»¶æ ååå¶å®;è´è´£ä¸»æ¿æ´ä½å¨ä»¶å¸å±,è¯ä¼°æ´æºç»æ;æ导layout走线,æ£æ¥pcb layout,æ导layout对åç§å¨ä»¶åæ åååº;

ãã5ã硬件è°è¯ä¸é®é¢åæ(åè½ãåèãå±ãæå头ãaudioã温åç);

ãã6ãè¯äº§ãé产ææ¯æ¯æ,ç¡®ä¿éäº§å¯¼å ¥ã

ãã7ãè¾åºç¸å ³ææ¯ææ¡£ãèµæãæ¥å;

ããæ 线é«çº§ç¡¬ä»¶å·¥ç¨å¸

ããä»»èè¦æ±:

ãã1ã大å¦æ¬ç§(å«)以ä¸å¦å,çµåä¿¡æ¯/éä¿¡å·¥ç¨/微波çµç£åºçç¸å ³ä¸ä¸,硬件å¼å5å¹´å以ä¸ç»éª;

ãã2ãææå®ççµè·¯ä¸ä¸ç论åºç¡;æåµå ¥å¼ç³»ç»å模æçµè·¯è®¾è®¡ç»éª;æè¯å¥½ç产åå¼åç»éª,å ·æ3个以ä¸äº§åå®æ´å¼åè¿ç¨çä¸ä¸ç»å;

ãã3ãç²¾étpãå±ãæå头ãçµæ± ãçµæºçé¨ä»¶ä¸çè³å°ä¸ä¸ªçåç以ååºç¨;

ãã4ãçæ硬件设计çåç§è®¾è®¡è½¯ä»¶;

ãã5ãçç»ä½¿ç¨åç§æµè¯ä»ªå¨åå·¥å ·,çææºè½ç»ç«¯å¯é æ§æµè¯ææ ;

ãã6ã端æ£çå·¥ä½æ度åè¯å¥½çæ²éè½å,è¯å¥½çæ§è¡è½ååå¢éåä½ç²¾ç¥;

ãã7ãä¸æ³¨äºå·¥ä½,以ç»æ为导åã

ããå²ä½èè´£:

ãã1ãåä¸é¡¹ç®ç«é¡¹,ç¡®å®é¡¹ç®å¹³å°éå;

ãã2ãè´è´£è®¾è®¡æ 线ç»ç«¯äº§å硬件æ»ä½æ¹æ¡å详ç»æ¹æ¡è®¾è®¡åç³»ç»åæ;

ãã3ãåä¸å å è¯å®¡ã项ç®éæ±è¯å®¡ãçµåå å¨ä»¶è¯å®¡;

ãã4ãè´è´£åçå¾ç设计ãbomå¨ä»¶æ ååå¶å®;è´è´£ä¸»æ¿æ´ä½å¨ä»¶å¸å±,è¯ä¼°æ´æºç»æ;æ导layout走线,æ£æ¥pcb layout,æ导layout对åç§å¨ä»¶åæ åååº;

ãã5ã硬件è°è¯ä¸é®é¢åæ(åè½ãåèãå±ãæå头ãaudioã温åç);

ãã6ãè¯äº§ãé产ææ¯æ¯æ,ç¡®ä¿éäº§å¯¼å ¥ã

ãã7ãè¾åºç¸å ³ææ¯ææ¡£ãèµæãæ¥å;

硬件工ç¨å¸å²ä½èè´£(ç¯)ãã硬件工ç¨å¸(pon)太ä»å¸åç»´çµåæéå ¬å¸å¤ªä»å¸åç»´çµåæéå ¬å¸,åç»´å²ä½èè´£:

ãã1ãè´è´£å ¬å¸ponç¸å ³äº§åç硬件设计åå¼å;

ãã2ãæç §é¡¹ç®è¦æ±å®ææ»ä½æ¹æ¡ãå¨ä»¶éåãåçå¾è¯¦ç»è®¾è®¡ãåæ¿é»è¾è®¾è®¡ãè°è¯ã解å³bugçå·¥ä½;

ãã3ãåæ¶å®æåç§ææ¡£åæ ååèµæçç¼å;

ããä»»èèµæ ¼:

ãã1ãçµåãèªå¨åçç¸å ³ä¸ä¸,è±æè½åè¾å¥½;

ãã2ãæ¬ç§ä¸å¹´ä»¥ä¸é讯æç½ç»äº§åç¸å ³å·¥ä½ç»éª;

ãã3ãå¨æ°åçµè·¯è®¾è®¡å°¤å ¶æ¯é«éæ°åçµè·¯æ¹é¢æ丰å¯çç»éª;

ãã4ãåºç¨è¿mips,armæpowerpcçåµå ¥å¼cpuç硬件å¼å;

ãã5ãææ¡verilogævhdlç硬件æè¿°è¯è¨è¿è¡cpldçå¼å;

ãã6ãä»äºè¿å æ¥å ¥,å 模å,switch,sdh,dslç产å硬件å¼åè ä¼å ;

ãã7ãçæ以太ç½ä»¥åvoipç¸å ³æ ååæ¶æä¼å ;

ãã8ãæè¯å¥½çå¢éç²¾ç¥ä»¥ååè¦èå³çåæ§,å·¥ä½è®¤ç,积æ主å¨,èªå¦è½åè¾å¥½ã

硬件工ç¨å¸å²ä½èè´£(ç¯)ããmtk硬件工ç¨å¸å ´å¤©å®ä¸(æ·±å³)æéå ¬å¸å ´å¤©å®ä¸(æ·±å³)æéå ¬å¸,å ´å¤©å®ä¸,å ´å¤©èä½æè¿°:

ãã1ãè´è´£mtkæ¹æ¡ç¡¬ä»¶ç³»ç»çµå设计;

ãã2ãè´è´£ç¡¬ä»¶å¨ä»¶éå,å¦ç³»ç»ä½¿ç¨çåç§ä¼ æå¨,驱å¨çµè·¯,æ§å¶çµè·¯çéå;

ãã3ãè´è´£ç¡¬ä»¶é¨åç°åºå®è£ ãè°è¯åç»´æ¤,åæµè¯å·¥ç¨å¸ä¸èµ·æ´ç确认产å硬件æµè¯è®¡ååç¸å ³ææ¡£ã

ããå²ä½è¦æ±:

ãã1ã计ç®æºä¸ç§ä»¥ä¸å¦å;

ãã2ãçæmtkæ¹æ¡äº§åçç¹æ®è®¾è®¡è¦æ±,è½æ ¹æ®è®¾è®¡å·®å¼å,éæ©ç¸åºé¨ä»¶æ¥æ»¡;

ãã3ã对mtkæ¹æ¡ç常ç¨çµè·¯,å æ¬:çµæºé¨å,é³è§é¢çµè·¯,çæ丰å¯ç设计ç»éªåç论åºç¡;

ãã4ãè½çç»ç使ç¨orcadæpadsçå·¥å ·è½¯ä»¶,æå¤å±pcbæ¿çå¼åè½ååå®é æä½è½å;

ãã5ãå ·å¤å¤å¹´é产产åç设计ç»éª,å¨æè½å强,è½çç»æä½å¸¸ç¨çåç§æµè¯ä»ªå¨åå·¥å ·ã

ãã6ãæä¸å¹´å·¥ä½ç»éªä»¥ä¸ã

硬件工ç¨å¸å²ä½èè´£(ç¯)ããåµå ¥å¼ç¡¬ä»¶å¼åå·¥ç¨å¸/å©ç(èä½ç¼å·:)æå·æ¼å®æºè½ç§ææéå ¬å¸æå·æ¼å®æºè½ç§ææéå ¬å¸,æ¼å®,æ¼å®æºè½,æ¼å®å²ä½æè¿°:

ãã1ãå®ç°åµå ¥å¼ç³»ç»;

ãã2ãå¼åãè°è¯ä¸ä½æºè½¯ç¡¬ä»¶;

ãã3ãä¸è½¯ä»¶é¨åäºæ²éåä½,ç解并å®ç°ä¸å¡åè½éæ±;

ãã4ãç¼åãç»´æ¤å¼åææ¡£,设计æµè¯ç¨ä¾ã

ããæèè¦æ±

ãã1ãæ¬ç§å以ä¸å¦å,计ç®æºãçµåä¿¡æ¯ãç²¾å¯ä»ªå¨çç¸å ³ä¸ä¸;

ãã2ãä¼ä½¿ç¨c/c++è¯è¨,å ·å¤è¯å¥½çç¼ç¨é£æ ¼;

ãã3ãææ¡ç¡¬ä»¶çæ¥è°è¯å·¥ä½,çæ硬件å¼åæµç¨;

ãã4ãè½ä½¿ç¨altium designerç»å¶pcbçä¼å èè;æc++ç¼åä¸ä½æºè½¯ä»¶ç»éªè ä¼å ;çæarmãdspç³»åçè¯ç使ç¨çä¼å èè

;FPGA高端项目:纯verilog的 G-UDP 高速协议栈,提供工程源码和技术支持

FPGA高端项目:纯verilog的 G-UDP 高速协议栈,提供工程源码和技术支持

前言:在现有的FPGA实现UDP方案中,我们面临以下几种常见挑战和局限性。首先,有一些方案使用verilog编写UDP收发器,但在其中使用了FIFO或RAM等IP,这种设计在实际项目中难以接受,因为它们缺乏基本的问题排查机制,例如ping功能。其次,网站影院源码有些方案具备ping功能,但代码不开源,用户无法获取源码,限制了问题调试和优化的可能性。第三,一些方案使用了Xilinx的Tri Mode Ethernet MAC三速网IP,尽管功能强大,但同样面临源码缺失的问题。第四,使用FPGA的GTX资源通过SFP光口实现UDP通信,这种方案便捷且无需额外网络变压器。最后,真正意义上的纯verilog实现的UDP协议栈,即全部代码均使用verilog编写,不依赖任何IP,这种方案在市面上较少见,且难以获取。

本设计采用纯verilog实现的G-UDP高速协议栈,专注于提供G-UDP回环通信测试。它旨在为用户提供一个高度可移植、功能丰富的G-UDP协议栈架构,支持用户根据需求创建自己的项目。该协议栈基于主流FPGA器件,提供了一系列工程源码,适用于Xilinx系列FPGA,使用Vivado作为开发工具。核心资源为GTY,同时支持SFP和QSFP光口。

经过多次测试,该协议栈稳定可靠,适用于教育、研究和工业应用领域,包括医疗和军用数字通信。用户可以轻松获取完整的工程源码和技术支持。本设计在遵守相关版权和使用条款的前提下,提供给个人学习和研究使用,禁止用于商业用途。

1G和G UDP协议栈版本介绍:本设计还提供了1G和G速率的UDP协议栈,包括数据回环、视频传输、命运wyd源码AD采集传输等应用。通过阅读相关博客,用户可以找到这些版本的工程源码和应用案例。

性能特点:本协议栈具有以下特性:

- 全部使用verilog编写,无任何IP核依赖。

- 高度可移植性,适用于不同FPGA型号。

- 强大的适应性,已成功测试在多种PHY上。

- 时序收敛良好。

- 包括动态ARP功能。

- 不具备ping功能。

- 用户接口数据位宽高达位。

- 最高支持G速率。

详细设计方案:设计基于FPGA板载的TI DPISRGZ网络芯片和QSFP光口,采用GTY+QSFP光口构建G-UDP高速协议栈,同时利用1G/2.5G Ethernet PHY和SGMII接口实现1G-UDP协议栈。设计包含两个UDP数据通路,分别支持G和1G速率,使用同一高速协议栈。代码中包含axis_adapter.v模块用于8位到位数据宽度的转换,以及axis_switch.v模块用于数据路径切换的仲裁。

网络调试助手:本设计提供了一个简单的回环测试工具,支持常用Windows软件,用于测试UDP数据收发。

高速接口资源使用:设计中涉及到G-UDP和1G-UDP数据通路的实现,包括GTY和1G/2.5G Ethernet PHY资源的调用,分别应用于不同速率的UDP通信。

详细实现方案:设计包含G-PHY层、G-MAC层、1G-MAC层、AXI4-Stream总线仲裁、AXI4-Stream FIFO、G-UDP高速协议栈等关键组件。每个模块都采用verilog实现,确保高性能和可移植性。

网络数据处理:设计中的G-PHY层处理GTY输出的数据,进行解码、对齐、校验等操作。1G-MAC层则将GMII数据转换为AXI4-Stream数据。协议栈包含动态ARP层、IP层、UDP层,实现标准UDP协议功能。

工程源码获取:对于感兴趣的开发者,可以获取完整的工程源码和技术支持。工程源码以某度网盘链接方式提供,确保用户能够轻松下载并进行移植和调试。

总结:本设计提供了一个强大、灵活的G-UDP高速协议栈解决方案,支持多种FPGA平台和PHY接口,适用于各种网络通信需求。通过提供的工程源码和技术支持,用户可以轻松地在自己的项目中集成和使用这些功能。

FPGA千兆网 UDP 网络视频传输,基于RTL PHY实现,提供工程和QT上位机源码加技术支持

前言:

探索使用FPGA实现千兆网UDP视频传输,本文采用基于RTL PHY芯片的设计,提供完整工程源码与QT上位机源码。本文主要针对FPGA开发者的实践指南,特别强调UDP协议栈的实现与优化。

设计思路框架:

本文设计的FPGA系统基于RTL PHY实现千兆网UDP视频传输,包含视频源选择、OV摄像头配置、动态彩条生成、UDP协议栈实现、IP地址与端口配置、QT上位机显示等功能。通过顶层的宏定义选择视频源,支持动态彩条与OV摄像头。

视频源选择与配置:

系统提供两种视频源选择:一是使用廉价的OV摄像头模组;二是内置动态彩条模拟视频,适用于无摄像头或无法接入摄像头的情况。选择逻辑通过顶层宏定义实现,默认选择OV摄像头。

OV摄像头配置与采集:

支持x分辨率的OV摄像头配置,输出RGB或RGB格式的视频数据,配置通过verilog代码模块实现。系统集成摄像头配置与视频采集功能,为视频传输提供稳定数据源。

动态彩条生成:

动态彩条模块可配置不同分辨率与参数,用于无摄像头输入时生成模拟视频数据。动态彩条通过FPGA内部产生,提供灵活的视频源选择。

UDP协议栈实现:

系统采用非开源的UDP协议栈,与Tri Mode Ethernet MAC三速网IP配合使用。协议栈提供用户接口,简化UDP协议实现,支持接收校验和检验、IP首部校验和生成、ARP请求与响应等功能。

数据缓冲与发送:

使用数据缓冲FIFO组实现UDP数据的高效传输,通过AXI-Stream接口与Tri Mode Ethernet MAC互联,支持时钟域与数据位宽转换,确保高效数据传输。

IP地址与端口号修改:

协议栈允许用户修改IP地址与端口号,适应不同网络环境的配置需求。

Tri Mode Ethernet MAC与RTL PHY移植:

设计使用Xilinx官方的Tri Mode Ethernet MAC IP核,针对RTL PHY进行移植优化,包括时钟域转换与数据位宽适配。移植注意事项包括版本一致性、FPGA型号调整、DDR配置与引脚约束修改等。

QT上位机与源码提供:

系统集成与QT上位机通信的用户接口,提供兼容x与P分辨率的QT上位机源码,支持视频抓取与显示功能。用户可根据需求修改代码以适应更高分辨率。

工程移植与调试:

本文提供详细的工程移植指南,包括vivado版本、FPGA型号、资源消耗与功耗分析。针对不同vivado版本、FPGA型号与DDR配置的移植策略,确保工程在不同环境下的稳定运行。

上板调试与演示:

本文指导开发板的连接与调试步骤,包括开发板与电脑的物理连接、IP地址配置与验证过程。通过ping测试确保网络连通性,提供静态与动态演示视频,直观展示视频传输流程。

福利与获取:

本文提供工程源码的获取方式,包括某度网盘链接分享。用户需通过私信或指定方式获取源码文件,以适应不同需求与环境的FPGA千兆网UDP视频传输项目。

FPGA纯verilog实现UDP协议栈,sgmii接口SFP光口收发,提供工程源码和技术支持

FPGA纯verilog实现的UDP协议栈和sgmii接口SFP光口收发功能,为用户提供工程源码和技术支持,旨在解决现有UDP解决方案的不足。

市面上的UDP实现方案存在缺陷,如一些仅实现基础功能而缺乏ping功能,或者虽有ping但不开源,难以排查问题。另一些方案虽功能全面,但依赖于需要许可证的IP核或不提供源码。本设计则与众不同,采用纯verilog编写,不依赖任何IP核,具有高度移植性和通用性。

设计特点包括:1)纯verilog实现,无IP核介入,支持1G速率;2)通过Xilinx的SGMII IP核实现网络PHY功能,通过SFP光口进行UDP数据传输;3)用户接口为AXIS,简化操作;4)经过充分测试,适用于多种FPGA平台,适用于医疗、军工等领域的数字通信应用。

具体设计细节涉及SFP接口对接、GMII AXIS接口模块、AXIS FIFO,以及完整的UDP协议栈,包括ARP、IP和UDP层的实现。此外,工程源码支持Vivado.1环境下,针对xc7ktffg-2开发板进行的上板调试和验证。

获取工程源码和技术支持的方式在文章末尾,通过私信或网盘链接提供,包括详细的上板调试步骤和资料。无论你是在校学生、研究生还是在职工程师,都能在该项目中找到所需资源,进行高效开发和验证。

FPGA 高端项目:基于 SGMII 接口的 UDP 协议栈,提供2套工程源码和技术支持

FPGA 高端项目:基于 SGMII 接口的 UDP 协议栈,提供2套工程源码和技术支持

前言:

在实现 UDP 协议栈的过程中,网上有许多可用的资源,但大多存在一些局限性,如功能不全面、缺乏源码或难以进行问题排查。本设计旨在填补这一空白,提供一个完整的、功能全面的 UDP 协议栈,以及可移植性强、适用于多种 FPGA 器件和开发环境的源码。

核心内容:

- **纯 verilog 实现**:本设计完全使用 verilog 语言编写,未依赖任何 IP 核,包括 FIFO 和 RAM 等,确保了协议栈的可移植性和自定义性。

- **源码和技术支持**:提供针对市面上主流 SGMII 接口的 PHY 芯片的两个 Vivado .2 版本的工程源码。

- **稳定性与可靠性**:经过大量测试的稳定可靠性能,可直接应用于项目中,适用于学生、研究生和在职工程师的开发需求。

- **适用范围**:适用于医疗、军工等行业的数字通信领域,支持多种 FPGA 器件和开发工具。

- **开源与版权**:提供完整的工程源码和技术支持,遵循个人学习和研究使用规定,禁止用于商业用途。

工程源码与技术支持:

工程源码分为两套,分别针对不同型号的 FPGA 和 PHY 芯片,适用于 Xilinx 和 Altera 等主要 FPGA 平台。提供详细的安装和移植指南,以及网络调试助手工具的使用说明。

性能亮点:

- **移植性**:纯 verilog 实现,无 IP 依赖,易于移植到不同 FPGA 平台。

- **适应性**:兼容多种 PHY 接口类型,包括 MII、GMII、RGMII、SGMII 等。

- **高性能**:最高支持 G 速率,适用于不同网络需求。

- **动态 ARP**:支持动态 ARP 功能,提高了网络通信的可靠性和效率。

详细设计方案:

设计采用两块 FPGA 板卡,分别搭载 DPISRGZ 和 E PHY 芯片,实现 SGMII 数据流的高效传输。通过一系列硬件组件(包括网络调试助手、PHY、FPGA 板卡等)的协同工作,实现数据的回环测试,确保协议栈的正确性和稳定性。

移植与调试:

提供详细的移植指南,包括不同 FPGA 型号和 Vivado 版本的适应策略。上板调试流程简单明了,包含准备工作、连接步骤和验证方法,确保用户能够顺利进行实际应用。

获取方式:

工程源码和相关文档以网盘链接形式提供,用户可自行下载使用。遵循版权规定,仅限个人学习和研究目的。如有任何疑问或需要进一步技术支持,可通过私信或评论方式与博主联系。

总结:

本项目旨在提供一个高度可移植、功能全面的 UDP 协议栈,以及丰富的源码和技术支持,旨在满足不同行业和领域对高效网络通信的需求。通过提供稳定可靠的工程源码和详细的移植指南,我们旨在简化开发流程,缩短项目周期,为开发者提供有力的技术支持。